- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC18F67K22-I/PTRSL (Microchip Technology)MCU PIC 128K FLASH XLP 64TQFP

P89V52X2_3

NXP B.V. 2009. All rights reserved.

Product data sheet

Rev. 03 — 4 May 2009

32 of 57

NXP Semiconductors

P89V52X2

80C51 with 256 B RAM, 192 B data EEPROM

6.12 Power-saving modes

The device provides two power saving modes of operation for applications where power

consumption is critical. The two modes are idle and Power-down, see Table 31.

6.12.1 Idle mode

Idle mode is entered setting the IDL bit in the PCON register. In Idle mode, the program

counter is stopped. The system clock continues to run and all interrupts and peripherals

remain active. The on-chip RAM and the special function registers hold their data during

this mode.

2

EX1

External Interrupt 1 Enable.

1

ET0

Timer 0 Overow Interrupt Enable.

0

EX0

External Interrupt 0 Enable.

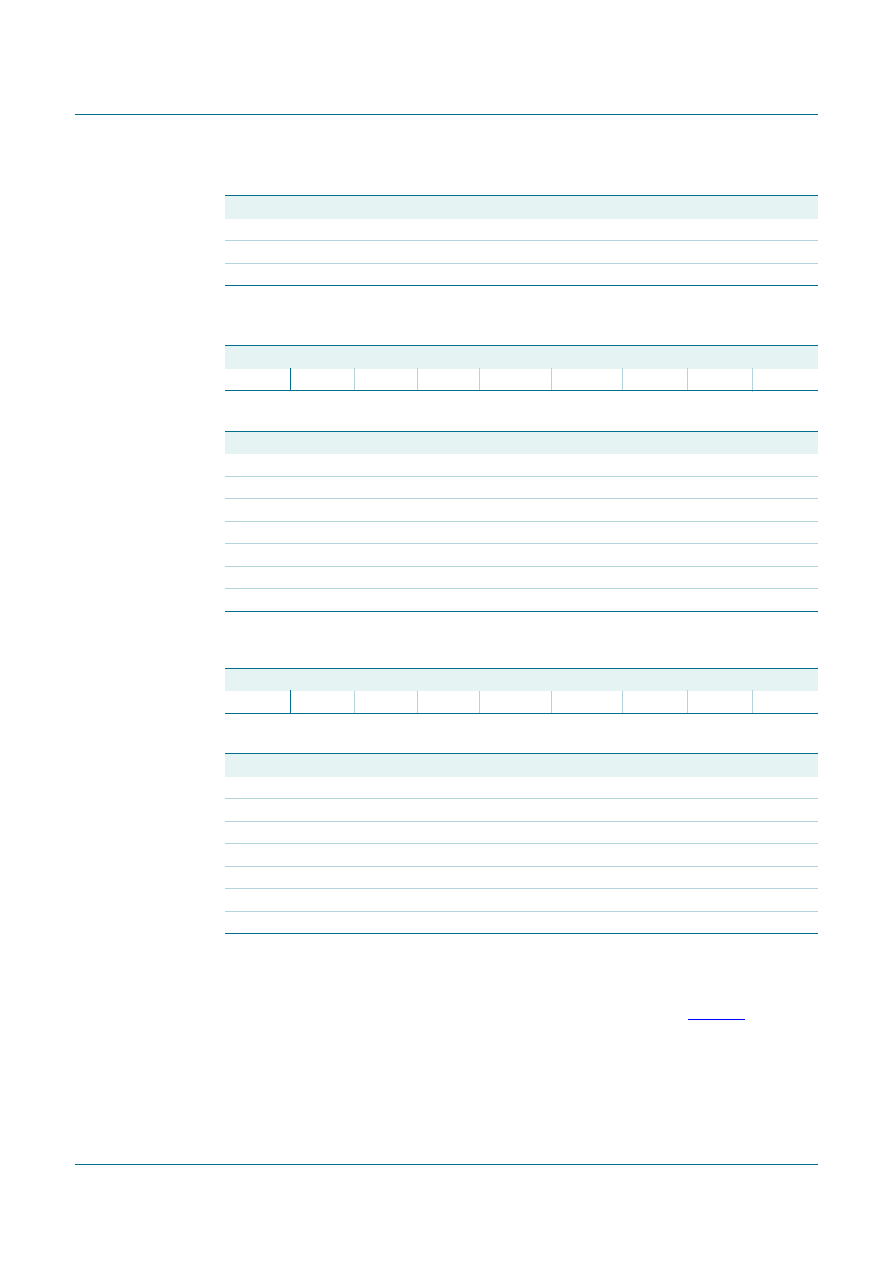

Table 27.

IP - Interrupt priority low register (address B8H) bit allocation

Bit addressable; Reset value: 00H

Bit

7

6

5

4

3

2

1

0

Symbol

-

PT2

PS

PT1

PX1

PT0

PX0

Table 28.

IP - Interrupt priority low register (address B8H) bit description

Bit

Symbol

Description

7:6

-

Reserved

5

PT2

Timer 2 Interrupt Priority Low Bit.

4

PS

Serial Port Interrupt Priority Low Bit.

3

PT1

Timer 1 Interrupt Priority Low Bit.

2

PX1

External Interrupt 1 Priority Low Bit.

1

PT0

Timer 0 Interrupt Priority Low Bit.

0

PX0

External Interrupt 0 Priority Low Bit.

Table 29.

IPH - Interrupt priority high register (address B7H) bit allocation

Not bit addressable; Reset value: 00H

Bit

7

6

5

4

3

2

1

0

Symbol

-

PT2H

PSH

PT1H

PX1H

PT0H

PX0H

Table 30.

IPH - Interrupt priority high register (address B7H) bit description

Bit

Symbol

Description

7:6

-

Reserved

5

PT2H

Timer 2 Interrupt Priority High Bit.

4

PSH

Serial Port Interrupt Priority High Bit.

3

PT1H

Timer 1 Interrupt Priority High Bit.

2

PX1H

External Interrupt 1 Priority High Bit.

1

PT0H

Timer 0 Interrupt Priority High Bit.

0

PX0H

External Interrupt 0 Priority High Bit.

Table 26.

IE - Interrupt enable register (address A8H) bit description …continued

Bit

Symbol

Description

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F66K90-I/MRRSL

MCU PIC 64K FLASH MEM XLP 64QFN

PIC16LC621-04/SO

IC MCU OTP 1KX14 COMP 18SOIC

PIC18LF2410-I/SP

IC MCU FLASH 8KX16 28-DIP

DSPIC30F3013-20I/SP

IC DSPIC MCU/DSP 24K 28DIP

PIC18LF6390-I/PT

IC PIC MCU FLASH 4KX16 64TQFP

DSPIC30F3013-30I/SP

IC DSPIC MCU/DSP 24K 28DIP

DSPIC33FJ32MC202-E/SO

IC DSPIC MCU/DSP 32K 28SOIC

52745-0896

CONN FFC 8POS .5MM R/A ZIF SMD

相关代理商/技术参数

PIC18F67K22-I/PTRSL

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 16MIPS 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 16MIPS, TQFP-64

PIC18F67K22T-I/MR

功能描述:8位微控制器 -MCU 128kB Flash 4kB RAM

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K22T-I/MRRSL

功能描述:8位微控制器 -MCU 128KB Flash 4KB RAM nanoWatt XLP GP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K22T-I/PT

功能描述:8位微控制器 -MCU 128kB Flash 4kB RAM

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K22T-I/PTRSL

功能描述:8位微控制器 -MCU 128KB Flash 4KB RAM nanoWatt XLP GP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K90-E/MR

功能描述:8位微控制器 -MCU 128KB Flash 4KB RAM LCD

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K90-E/PT

功能描述:8位微控制器 -MCU 128KB Flash 4KB RAM LCD

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F67K90-I/MR

功能描述:8位微控制器 -MCU 128kB Flash 4kB RAM LCD

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT